សេចក្តីសង្ខេបនៃបន្ទះ SiC

បន្ទះស៊ីលីកុនកាបៃ (SiC)បានក្លាយជាស្រទាប់ខាងក្រោមដែលត្រូវបានជ្រើសរើសសម្រាប់ឧបករណ៍អេឡិចត្រូនិចដែលមានថាមពលខ្ពស់ ប្រេកង់ខ្ពស់ និងសីតុណ្ហភាពខ្ពស់នៅទូទាំងវិស័យយានយន្ត ថាមពលកកើតឡើងវិញ និងអាកាសចរណ៍។ ផលប័ត្ររបស់យើងគ្របដណ្តប់លើពហុប្រភេទសំខាន់ៗ និងគ្រោងការណ៍ដូប៉ាំង — 4H ដែលមានដូប៉ាំងអាសូត (4H-N) អ៊ីសូឡង់ពាក់កណ្តាលភាពបរិសុទ្ធខ្ពស់ (HPSI) 3C ដែលមានដូប៉ាំងអាសូត (3C-N) និងប្រភេទ p 4H/6H (4H/6H-P) — ផ្តល់ជូនជាថ្នាក់គុណភាពបី៖ PRIME (ស្រទាប់ខាងក្រោមប៉ូលាទាំងស្រុង ថ្នាក់ឧបករណ៍) DUMMY (លាប ឬមិនប៉ូលាសម្រាប់ការសាកល្បងដំណើរការ) និង RESEARCH (ស្រទាប់អេពីផ្ទាល់ខ្លួន និងទម្រង់ដូប៉ាំងសម្រាប់ការស្រាវជ្រាវ និងអភិវឌ្ឍន៍)។ អង្កត់ផ្ចិតបន្ទះមានទំហំ 2″, 4″, 6″, 8″ និង 12″ ដើម្បីឱ្យសមនឹងឧបករណ៍ចាស់ៗ និងរោងចក្រទំនើបៗ។ យើងក៏ផ្គត់ផ្គង់ប៊ូលម៉ូណូគ្រីស្តាលីន និងគ្រីស្តាល់គ្រាប់ពូជដែលមានទិសដៅជាក់លាក់ ដើម្បីគាំទ្រដល់ការលូតលាស់គ្រីស្តាល់ផ្ទៃក្នុងផងដែរ។

បន្ទះសៀគ្វី 4H-N របស់យើងមានដង់ស៊ីតេផ្ទុកចាប់ពី 1×10¹⁶ ដល់ 1×10¹⁹ cm⁻³ និងភាពធន់នៃ 0.01–10 Ω·cm⁻³ ដែលផ្តល់នូវការចល័តអេឡិចត្រុងដ៏ល្អឥតខ្ចោះ និងវាលបំបែកលើសពី 2 MV/cm—ដែលល្អសម្រាប់ឌីយ៉ូត Schottky, MOSFETs និង JFETs។ ស្រទាប់ខាងក្រោម HPSI លើសពីភាពធន់ 1×10¹² Ω·cm⁻² ជាមួយនឹងដង់ស៊ីតេមីក្រូភីបក្រោម 0.1 cm⁻² ដែលធានាបាននូវការលេចធ្លាយតិចតួចបំផុតសម្រាប់ឧបករណ៍ RF និងមីក្រូវ៉េវ។ Cubic 3C-N ដែលមានក្នុងទម្រង់ 2″ និង 4″ អាចឱ្យមានភាពខុសប្លែកគ្នាលើស៊ីលីកុន និងគាំទ្រកម្មវិធីហ្វូតូនិក និង MEMS ថ្មី។ បន្ទះសៀគ្វីប្រភេទ P 4H/6H-P ដែលបន្ថែមជាមួយអាលុយមីញ៉ូមដល់ 1×10¹⁶–5×10¹⁸ cm⁻³ ជួយសម្រួលដល់ស្ថាបត្យកម្មឧបករណ៍បំពេញបន្ថែម។

បន្ទះសៀគ្វី SiC និងបន្ទះសៀគ្វី PRIME ឆ្លងកាត់ការប៉ូលាគីមី-មេកានិចរហូតដល់ភាពរដុបនៃផ្ទៃ RMS <0.2 nm ការប្រែប្រួលកម្រាស់សរុបក្រោម 3 µm និងធ្នូ <10 µm។ ស្រទាប់ខាងក្រោម DUMMY បង្កើនល្បឿនការធ្វើតេស្តការផ្គុំ និងការធ្វើតេស្តវេចខ្ចប់ ខណៈពេលដែលបន្ទះសៀគ្វី RESEARCH មានកម្រាស់ស្រទាប់អេពីពី 2–30 µm និងការប្រើប្រាស់សារធាតុដូបតាមតម្រូវការ។ ផលិតផលទាំងអស់ត្រូវបានបញ្ជាក់ដោយការឌីផ្រាក់ស្យុងកាំរស្មីអ៊ិច (ខ្សែកោងរញ្ជួយ <30 arcsec) និងវិសាលគមរ៉ាម៉ាន ជាមួយនឹងការធ្វើតេស្តអគ្គិសនី—ការវាស់វែងសាល ការវិភាគទម្រង់ C–V និងការស្កេនមីក្រូភីប—ធានានូវការអនុលោមតាម JEDEC និង SEMI។

គ្រាប់ប៊ូលដែលមានអង្កត់ផ្ចិតរហូតដល់ 150 មីលីម៉ែត្រ ត្រូវបានដាំដុះតាមរយៈ PVT និង CVD ជាមួយនឹងដង់ស៊ីតេនៃការផ្លាស់ទីលំនៅក្រោម 1×10³ សង់ទីម៉ែត្រ⁻² និងចំនួនមីក្រូភីបទាប។ គ្រីស្តាល់គ្រាប់ពូជត្រូវបានកាត់ក្នុងរង្វង់ 0.1° ពីអ័ក្ស c ដើម្បីធានាការលូតលាស់ដែលអាចបង្កើតឡើងវិញបាន និងទិន្នផលកាត់ខ្ពស់។

តាមរយៈការរួមបញ្ចូលគ្នានូវប៉ូលីធីបច្រើន វ៉ារ្យ៉ង់ដូពីង ថ្នាក់គុណភាព ទំហំបន្ទះ SiC និងការផលិតប៊ូល និងគ្រីស្តាល់គ្រាប់ពូជនៅក្នុងក្រុមហ៊ុន វេទិកាស្រទាប់ SiC របស់យើងធ្វើឱ្យខ្សែសង្វាក់ផ្គត់ផ្គង់មានភាពសាមញ្ញ និងបង្កើនល្បឿនការអភិវឌ្ឍឧបករណ៍សម្រាប់យានយន្តអគ្គិសនី បណ្តាញឆ្លាតវៃ និងកម្មវិធីបរិស្ថានដ៏អាក្រក់។

សេចក្តីសង្ខេបនៃបន្ទះ SiC

បន្ទះស៊ីលីកុនកាបៃ (SiC)បានក្លាយជាស្រទាប់ខាងក្រោម SiC ដែលត្រូវបានជ្រើសរើសសម្រាប់ឧបករណ៍អេឡិចត្រូនិចដែលមានថាមពលខ្ពស់ ប្រេកង់ខ្ពស់ និងសីតុណ្ហភាពខ្ពស់នៅទូទាំងវិស័យយានយន្ត ថាមពលកកើតឡើងវិញ និងវិស័យអាកាសចរណ៍។ ផលប័ត្ររបស់យើងគ្របដណ្តប់លើពហុប្រភេទសំខាន់ៗ និងគ្រោងការណ៍ដូប — 4H ដែលមានដូបអាសូត (4H-N) ពាក់កណ្តាលអ៊ីសូឡង់ភាពបរិសុទ្ធខ្ពស់ (HPSI) 3C ដែលមានដូបអាសូត (3C-N) និងប្រភេទ p 4H/6H (4H/6H-P) — ផ្តល់ជូនជាថ្នាក់គុណភាពបី៖ បន្ទះ SiCPRIME (ប៉ូលាទាំងស្រុង ស្រទាប់ខាងក្រោមកម្រិតឧបករណ៍) DUMMY (លាប ឬមិនប៉ូលាសម្រាប់ការសាកល្បងដំណើរការ) និង RESEARCH (ស្រទាប់ Epi ផ្ទាល់ខ្លួន និងទម្រង់ដូពីងសម្រាប់ R&D)។ អង្កត់ផ្ចិតបន្ទះ SiC មានទំហំ 2", 4", 6", 8", និង 12" ដើម្បីឲ្យសមស្របទាំងឧបករណ៍ចាស់ៗ និងរោងចក្រទំនើបៗ។ យើងក៏ផ្គត់ផ្គង់ប៊ូលម៉ូណូគ្រីស្តាលីន និងគ្រីស្តាល់គ្រាប់ពូជដែលមានទិសដៅជាក់លាក់ ដើម្បីគាំទ្រដល់ការលូតលាស់គ្រីស្តាល់ផ្ទៃក្នុងផងដែរ។

បន្ទះសៀគ្វី SiC 4H-N របស់យើងមានដង់ស៊ីតេផ្ទុកចាប់ពី 1×10¹⁶ ដល់ 1×10¹⁹ cm⁻³ និងភាពធន់នៃ 0.01–10 Ω·cm⁻³ ដែលផ្តល់នូវការចល័តអេឡិចត្រុងដ៏ល្អឥតខ្ចោះ និងវាលបំបែកលើសពី 2 MV/cm—ដែលល្អសម្រាប់ឌីយ៉ូត Schottky, MOSFETs និង JFETs។ ស្រទាប់ខាងក្រោម HPSI លើសពីភាពធន់ 1×10¹² Ω·cm⁻² ជាមួយនឹងដង់ស៊ីតេមីក្រូភីបក្រោម 0.1 cm⁻² ដែលធានាបាននូវការលេចធ្លាយតិចតួចបំផុតសម្រាប់ឧបករណ៍ RF និងមីក្រូវ៉េវ។ គូប 3C-N ដែលមានក្នុងទម្រង់ 2″ និង 4″ អនុញ្ញាតឱ្យមាន heteroepitaxy លើស៊ីលីកុន និងគាំទ្រកម្មវិធីហ្វូតូនិក និង MEMS ថ្មី។ បន្ទះសៀគ្វី SiC ប្រភេទ P-type 4H/6H-P ដែលបន្ថែមជាមួយអាលុយមីញ៉ូមដល់ 1×10¹⁶–5×10¹⁸ cm⁻³ ជួយសម្រួលដល់ស្ថាបត្យកម្មឧបករណ៍បំពេញបន្ថែម។

បន្ទះសៀគ្វី SiC PRIME ឆ្លងកាត់ការប៉ូលាគីមី-មេកានិចរហូតដល់ភាពរដុបនៃផ្ទៃ RMS <0.2 nm ការប្រែប្រួលកម្រាស់សរុបក្រោម 3 µm និងធ្នូ <10 µm។ ស្រទាប់ខាងក្រោម DUMMY បង្កើនល្បឿនការធ្វើតេស្តការផ្គុំ និងការធ្វើតេស្តវេចខ្ចប់ ខណៈពេលដែលបន្ទះសៀគ្វី RESEARCH មានកម្រាស់ស្រទាប់អេពីពី 2–30 µm និងការប្រើប្រាស់សារធាតុដូបតាមតម្រូវការ។ ផលិតផលទាំងអស់ត្រូវបានបញ្ជាក់ដោយការឌីផ្រាក់ស្យុងកាំរស្មីអ៊ិច (ខ្សែកោងរញ្ជួយ <30 arcsec) និងវិសាលគមរ៉ាម៉ាន ជាមួយនឹងការធ្វើតេស្តអគ្គិសនី—ការវាស់វែងសាល ការវិភាគទម្រង់ C–V និងការស្កេនមីក្រូភីប—ធានានូវការអនុលោមតាម JEDEC និង SEMI។

គ្រាប់ប៊ូលដែលមានអង្កត់ផ្ចិតរហូតដល់ 150 មីលីម៉ែត្រ ត្រូវបានដាំដុះតាមរយៈ PVT និង CVD ជាមួយនឹងដង់ស៊ីតេនៃការផ្លាស់ទីលំនៅក្រោម 1×10³ សង់ទីម៉ែត្រ⁻² និងចំនួនមីក្រូភីបទាប។ គ្រីស្តាល់គ្រាប់ពូជត្រូវបានកាត់ក្នុងរង្វង់ 0.1° ពីអ័ក្ស c ដើម្បីធានាការលូតលាស់ដែលអាចបង្កើតឡើងវិញបាន និងទិន្នផលកាត់ខ្ពស់។

តាមរយៈការរួមបញ្ចូលគ្នានូវប៉ូលីធីបច្រើន វ៉ារ្យ៉ង់ដូពីង ថ្នាក់គុណភាព ទំហំបន្ទះ SiC និងការផលិតប៊ូល និងគ្រីស្តាល់គ្រាប់ពូជនៅក្នុងក្រុមហ៊ុន វេទិកាស្រទាប់ SiC របស់យើងធ្វើឱ្យខ្សែសង្វាក់ផ្គត់ផ្គង់មានភាពសាមញ្ញ និងបង្កើនល្បឿនការអភិវឌ្ឍឧបករណ៍សម្រាប់យានយន្តអគ្គិសនី បណ្តាញឆ្លាតវៃ និងកម្មវិធីបរិស្ថានដ៏អាក្រក់។

សន្លឹកទិន្នន័យបន្ទះសៀគ្វី SiC ប្រភេទ 4H-N ទំហំ 6 អ៊ីញ

| សន្លឹកទិន្នន័យបន្ទះ SiC ទំហំ 6 អ៊ីញ | ||||

| ប៉ារ៉ាម៉ែត្រ | ប៉ារ៉ាម៉ែត្ររង | ថ្នាក់ Z | ថ្នាក់ P | ថ្នាក់ D |

| អង្កត់ផ្ចិត | ១៤៩.៥–១៥០.០ ម.ម. | ១៤៩.៥–១៥០.០ ម.ម. | ១៤៩.៥–១៥០.០ ម.ម. | |

| កម្រាស់ | 4H-N | ៣៥០ មីក្រូម៉ែត្រ ± ១៥ មីក្រូម៉ែត្រ | ៣៥០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ | ៣៥០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ |

| កម្រាស់ | 4H-SI | ៥០០ មីក្រូម៉ែត្រ ± ១៥ មីក្រូម៉ែត្រ | ៥០០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ | ៥០០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ |

| ការតំរង់ទិសបន្ទះ | អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ <១១-២០> ±០.៥° (៤H-N); លើអ័ក្ស៖ <០០០១> ±០.៥° (៤H-SI) | អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ <១១-២០> ±០.៥° (៤H-N); លើអ័ក្ស៖ <០០០១> ±០.៥° (៤H-SI) | អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ <១១-២០> ±០.៥° (៤H-N); លើអ័ក្ស៖ <០០០១> ±០.៥° (៤H-SI) | |

| ដង់ស៊ីតេមីក្រូភីភី | 4H-N | ≤ ០.២ សង់ទីម៉ែត្រ² | ≤ 2 សង់ទីម៉ែត្រ⁻² | ≤ ១៥ សង់ទីម៉ែត្រ² |

| ដង់ស៊ីតេមីក្រូភីភី | 4H-SI | ≤ 1 សង់ទីម៉ែត្រ⁻² | ≤ 5 សង់ទីម៉ែត្រ⁻² | ≤ ១៥ សង់ទីម៉ែត្រ² |

| ភាពធន់ | 4H-N | ០.០១៥–០.០២៤ អូម·សង់ទីម៉ែត្រ | ០.០១៥–០.០២៨ អូម·សង់ទីម៉ែត្រ | ០.០១៥–០.០២៨ អូម·សង់ទីម៉ែត្រ |

| ភាពធន់ | 4H-SI | ≥ 1×10¹⁰ Ω·សង់ទីម៉ែត្រ | ≥ 1×10⁵ Ω·សង់ទីម៉ែត្រ | |

| ទិសដៅសំប៉ែតចម្បង | [១០-១០] ± ៥.០° | [១០-១០] ± ៥.០° | [១០-១០] ± ៥.០° | |

| ប្រវែងសំប៉ែតបឋម | 4H-N | ៤៧.៥ ម.ម ± ២.០ ម.ម | ||

| ប្រវែងសំប៉ែតបឋម | 4H-SI | ស្នាមរន្ធ | ||

| ការដកចេញគែម | ៣ ម.ម. | |||

| Warp/LTV/TTV/Bow | ≤2.5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| ភាពរដុប | ប៉ូឡូញ | Ra ≤ 1 nm | ||

| ភាពរដុប | ស៊ីអឹមភី | Ra ≤ 0.2 nm | Ra ≤ 0.5 nm | |

| ស្នាមប្រេះគែម | គ្មាន | ប្រវែងសរុប ≤ 20 ម.ម, តែមួយ ≤ 2 ម.ម | ||

| ចានឆកោន | ផ្ទៃសរុប ≤ 0.05% | ផ្ទៃសរុប ≤ 0.1% | ផ្ទៃសរុប ≤ 1% | |

| តំបន់ពហុប្រភេទ | គ្មាន | ផ្ទៃសរុប ≤ 3% | ផ្ទៃសរុប ≤ 3% | |

| ការរួមបញ្ចូលកាបូន | ផ្ទៃសរុប ≤ 0.05% | ផ្ទៃសរុប ≤ 3% | ||

| ស្នាមឆ្កូតលើផ្ទៃ | គ្មាន | ប្រវែងសរុប ≤ 1 × អង្កត់ផ្ចិតបន្ទះ | ||

| បន្ទះឈីបគែម | គ្មានអ្វីត្រូវបានអនុញ្ញាតទេ ≥ 0.2 ម.ម ទទឹង និងជម្រៅ | រហូតដល់ 7 បន្ទះឈីប, ≤ 1 ម.ម ក្នុងមួយបន្ទះ | ||

| TSD (ការផ្លាស់ទីលំនៅវីសដោយខ្សែ) | ≤ ៥០០ សង់ទីម៉ែត្រ² | គ្មាន | ||

| ការផ្លាស់ទីលំនៅរបស់ប្លង់មូលដ្ឋាន (BPD) | ≤ ១០០០ សង់ទីម៉ែត្រ² | គ្មាន | ||

| ការបំពុលផ្ទៃ | គ្មាន | |||

| ការវេចខ្ចប់ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | |

សន្លឹកទិន្នន័យបន្ទះសៀគ្វី SiC ប្រភេទ 4H-N ទំហំ 4 អ៊ីញ

| សន្លឹកទិន្នន័យបន្ទះ SiC ទំហំ 4 អ៊ីញ | |||

| ប៉ារ៉ាម៉ែត្រ | ផលិតកម្ម MPD សូន្យ | ថ្នាក់ផលិតកម្មស្តង់ដារ (ថ្នាក់ P) | ថ្នាក់ D (ថ្នាក់ D) |

| អង្កត់ផ្ចិត | ៩៩.៥ ម.ម.–១០០.០ ម.ម. | ||

| កម្រាស់ (4H-N) | ៣៥០ មីក្រូម៉ែត្រ ± ១៥ មីក្រូម៉ែត្រ | ៣៥០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ | |

| កម្រាស់ (4H-Si) | ៥០០ មីក្រូម៉ែត្រ ± ១៥ មីក្រូម៉ែត្រ | ៥០០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ | |

| ការតំរង់ទិសបន្ទះ | អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ <១១២០> ±០.៥° សម្រាប់ 4H-N; លើអ័ក្ស៖ <០០០១> ±០.៥° សម្រាប់ 4H-Si | ||

| ដង់ស៊ីតេមីក្រូបំពង់ (4H-N) | ≤0.2 សង់ទីម៉ែត្រ² | ≤2 សង់ទីម៉ែត្រ⁻² | ≤១៥ សង់ទីម៉ែត្រ² |

| ដង់ស៊ីតេមីក្រូបំពង់ (4H-Si) | ≤1 សង់ទីម៉ែត្រ⁻² | ≤5 សង់ទីម៉ែត្រ⁻² | ≤១៥ សង់ទីម៉ែត្រ² |

| ភាពធន់ (4H-N) | ០.០១៥–០.០២៤ អូម·សង់ទីម៉ែត្រ | ០.០១៥–០.០២៨ អូម·សង់ទីម៉ែត្រ | |

| ភាពធន់ (4H-Si) | ≥1E10 Ω·សង់ទីម៉ែត្រ | ≥1E5 Ω·សង់ទីម៉ែត្រ | |

| ទិសដៅសំប៉ែតចម្បង | [១០-១០] ±៥.០° | ||

| ប្រវែងសំប៉ែតបឋម | ៣២.៥ ម.ម ±២.០ ម.ម | ||

| ប្រវែងរាបស្មើបន្ទាប់បន្សំ | ១៨.០ ម.ម ±២.០ ម.ម | ||

| ទិសដៅរាបស្មើបន្ទាប់បន្សំ | ស៊ីលីកុនបែរមុខឡើងលើ៖ ៩០° CW ពីផ្ទៃរាបស្មើចម្បង ±៥.០° | ||

| ការដកចេញគែម | ៣ ម.ម. | ||

| LTV/TTV/Bow Warp | ≤2.5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ភាពរដុប | ប៉ូលា Ra ≤1 nm; CMP Ra ≤0.2 nm | Ra ≤0.5 nm | |

| ស្នាមប្រេះគែមដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | គ្មាន | ប្រវែងសរុប ≤10 ម.ម.; ប្រវែងតែមួយ ≤2 ម.ម. |

| បន្ទះ Hex ដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤0.1% |

| តំបន់ពហុប្រភេទដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ផ្ទៃសរុប ≤3% | |

| ការរួមបញ្ចូលកាបូនដែលមើលឃើញ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤3% | |

| ស្នាមឆ្កូតលើផ្ទៃស៊ីលីកុនដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ប្រវែងសរុប ≤1 អង្កត់ផ្ចិតបន្ទះសៀគ្វី | |

| បន្ទះសៀគ្វីគែមដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មានអ្វីត្រូវបានអនុញ្ញាតទេ ≥0.2 ម.ម ទទឹង និងជម្រៅ | អនុញ្ញាត 5, ≤1 ម.ម ក្នុងមួយៗ | |

| ការបំពុលផ្ទៃស៊ីលីកុនដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ||

| ការផ្លាស់ទីលំនៅរបស់វីស | ≤៥០០ សង់ទីម៉ែត្រ² | គ្មាន | |

| ការវេចខ្ចប់ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ |

សន្លឹកទិន្នន័យបន្ទះ SiC ប្រភេទ HPSI ទំហំ 4 អ៊ីញ

| សន្លឹកទិន្នន័យបន្ទះ SiC ប្រភេទ HPSI ទំហំ 4 អ៊ីញ | |||

| ប៉ារ៉ាម៉ែត្រ | ថ្នាក់ផលិតកម្ម MPD សូន្យ (ថ្នាក់ Z) | ថ្នាក់ផលិតកម្មស្តង់ដារ (ថ្នាក់ P) | ថ្នាក់ D (ថ្នាក់ D) |

| អង្កត់ផ្ចិត | ៩៩.៥–១០០.០ ម.ម. | ||

| កម្រាស់ (4H-Si) | ៥០០ មីក្រូម៉ែត្រ ±២០ មីក្រូម៉ែត្រ | ៥០០ មីក្រូម៉ែត្រ ±២៥ មីក្រូម៉ែត្រ | |

| ការតំរង់ទិសបន្ទះ | អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ <១១-២០> ±០.៥° សម្រាប់ 4H-N; លើអ័ក្ស៖ <០០០១> ±០.៥° សម្រាប់ 4H-Si | ||

| ដង់ស៊ីតេមីក្រូបំពង់ (4H-Si) | ≤1 សង់ទីម៉ែត្រ⁻² | ≤5 សង់ទីម៉ែត្រ⁻² | ≤១៥ សង់ទីម៉ែត្រ² |

| ភាពធន់ (4H-Si) | ≥1E9 Ω·សង់ទីម៉ែត្រ | ≥1E5 Ω·សង់ទីម៉ែត្រ | |

| ទិសដៅសំប៉ែតចម្បង | (១០-១០) ±៥.០° | ||

| ប្រវែងសំប៉ែតបឋម | ៣២.៥ ម.ម ±២.០ ម.ម | ||

| ប្រវែងរាបស្មើបន្ទាប់បន្សំ | ១៨.០ ម.ម ±២.០ ម.ម | ||

| ទិសដៅរាបស្មើបន្ទាប់បន្សំ | ស៊ីលីកុនបែរមុខឡើងលើ៖ ៩០° CW ពីផ្ទៃរាបស្មើចម្បង ±៥.០° | ||

| ការដកចេញគែម | ៣ ម.ម. | ||

| LTV/TTV/Bow Warp | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ភាពរដុប (មុខ C) | ប៉ូឡូញ | Ra ≤1 nm | |

| ភាពរដុប (មុខ Si) | ស៊ីអឹមភី | Ra ≤0.2 nm | Ra ≤0.5 nm |

| ស្នាមប្រេះគែមដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ប្រវែងសរុប ≤10 ម.ម.; ប្រវែងតែមួយ ≤2 ម.ម. | |

| បន្ទះ Hex ដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤0.1% |

| តំបន់ពហុប្រភេទដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ផ្ទៃសរុប ≤3% | |

| ការរួមបញ្ចូលកាបូនដែលមើលឃើញ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤3% | |

| ស្នាមឆ្កូតលើផ្ទៃស៊ីលីកុនដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ប្រវែងសរុប ≤1 អង្កត់ផ្ចិតបន្ទះសៀគ្វី | |

| បន្ទះសៀគ្វីគែមដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មានអ្វីត្រូវបានអនុញ្ញាតទេ ≥0.2 ម.ម ទទឹង និងជម្រៅ | អនុញ្ញាត 5, ≤1 ម.ម ក្នុងមួយៗ | |

| ការបំពុលផ្ទៃស៊ីលីកុនដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | គ្មាន | |

| ការផ្លាស់ទីលំនៅវីសដោយសារខ្សែស្រឡាយ | ≤៥០០ សង់ទីម៉ែត្រ² | គ្មាន | |

| ការវេចខ្ចប់ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | ||

ការអនុវត្តបន្ទះ SiC

-

ម៉ូឌុលថាមពល SiC Wafer សម្រាប់ឧបករណ៍បម្លែង EV

MOSFETs និងឌីយ៉ូដដែលមានមូលដ្ឋានលើបន្ទះសៀគ្វី SiC ដែលបង្កើតឡើងលើស្រទាប់សៀគ្វី SiC ដែលមានគុណភាពខ្ពស់ផ្តល់នូវការខាតបង់ប្តូរទាបបំផុត។ ដោយប្រើប្រាស់បច្ចេកវិទ្យាបន្ទះសៀគ្វី SiC ម៉ូឌុលថាមពលទាំងនេះដំណើរការនៅវ៉ុល និងសីតុណ្ហភាពខ្ពស់ ដែលអាចឱ្យឧបករណ៍បម្លែងចរន្តអគ្គិសនីមានប្រសិទ្ធភាពជាងមុន។ ការបញ្ចូលបន្ទះសៀគ្វី SiC ទៅក្នុងដំណាក់កាលថាមពលកាត់បន្ថយតម្រូវការត្រជាក់ និងទំហំដែលបង្ហាញពីសក្តានុពលពេញលេញនៃការច្នៃប្រឌិតបន្ទះសៀគ្វី SiC។ -

ឧបករណ៍ RF ប្រេកង់ខ្ពស់ និង 5G នៅលើ SiC Wafer

ឧបករណ៍ពង្រីកសំឡេង RF និងកុងតាក់ដែលផលិតនៅលើវេទិកាបន្ទះសៀគ្វី SiC ពាក់កណ្តាលអ៊ីសូឡង់បង្ហាញពីចរន្តកំដៅ និងវ៉ុលបំបែកខ្ពស់ជាង។ ស្រទាប់ខាងក្រោមបន្ទះសៀគ្វី SiC កាត់បន្ថយការខាតបង់ឌីអេឡិចត្រិចនៅប្រេកង់ GHz ខណៈពេលដែលកម្លាំងសម្ភារៈរបស់បន្ទះសៀគ្វី SiC អនុញ្ញាតឱ្យមានប្រតិបត្តិការដែលមានស្ថេរភាពក្រោមលក្ខខណ្ឌថាមពលខ្ពស់ និងសីតុណ្ហភាពខ្ពស់ — ដែលធ្វើឱ្យបន្ទះសៀគ្វី SiC ក្លាយជាស្រទាប់ខាងក្រោមដែលត្រូវបានជ្រើសរើសសម្រាប់ស្ថានីយ៍មូលដ្ឋាន 5G ជំនាន់ក្រោយ និងប្រព័ន្ធរ៉ាដា។ -

ស្រទាប់អុបតូអេឡិចត្រូនិច និង LED ពីបន្ទះ SiC

អំពូល LED ពណ៌ខៀវ និងអំពូល UV ដែលដាំដុះលើស្រទាប់ខាងក្រោមបន្ទះ SiC ទទួលបានអត្ថប្រយោជន៍ពីការផ្គូផ្គងបន្ទះឈើ និងការរលាយកំដៅដ៏ល្អឥតខ្ចោះ។ ការប្រើប្រាស់បន្ទះ SiC ដែលមានមុខរាងអក្សរ C ប៉ូលាធានាបាននូវស្រទាប់ epitaxial ឯកសណ្ឋាន ខណៈពេលដែលភាពរឹងដែលមាននៅក្នុងបន្ទះ SiC អនុញ្ញាតឱ្យបន្ទះស្តើងល្អ និងការវេចខ្ចប់ឧបករណ៍ដែលអាចទុកចិត្តបាន។ នេះធ្វើឱ្យបន្ទះ SiC ក្លាយជាវេទិកាដែលពេញនិយមសម្រាប់កម្មវិធី LED ដែលមានថាមពលខ្ពស់ និងមានអាយុកាលប្រើប្រាស់បានយូរ។

សំណួរ និងចម្លើយអំពីបន្ទះ SiC

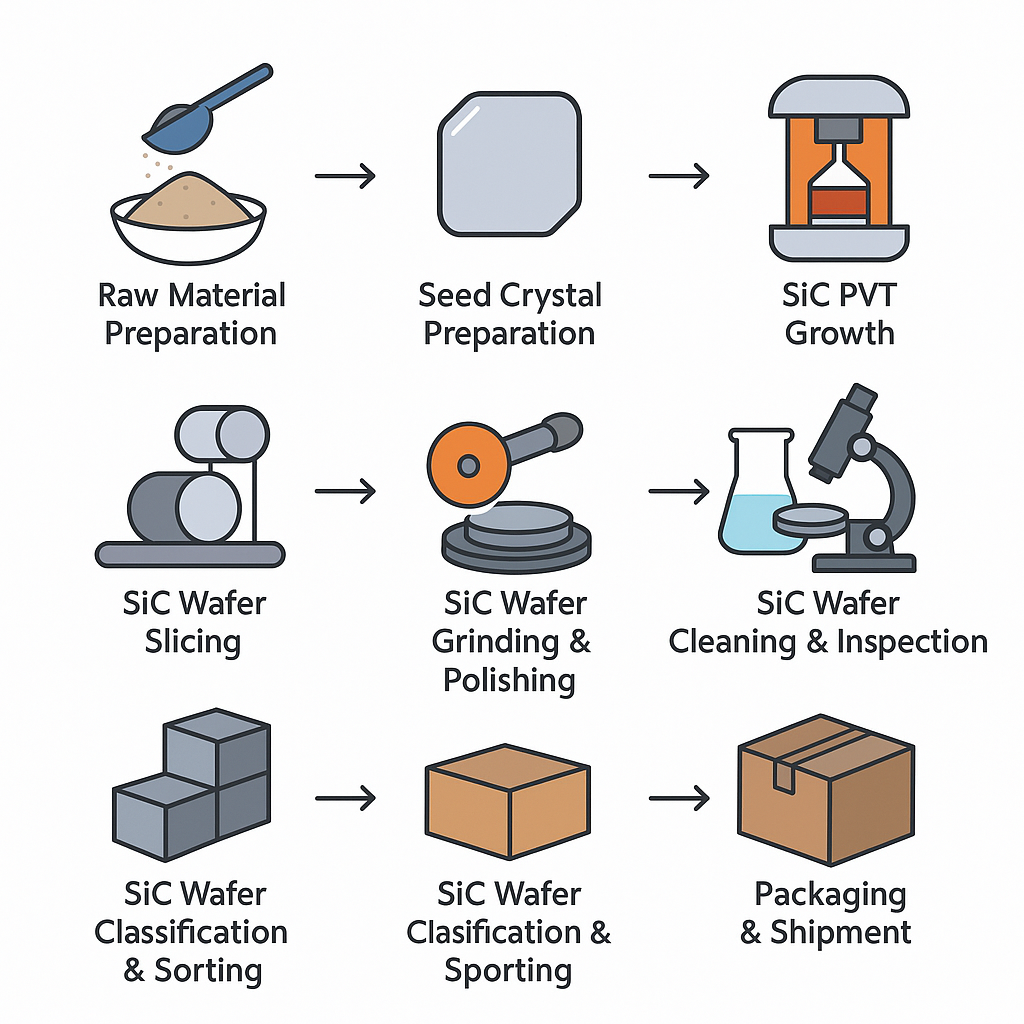

១. សំណួរ៖ តើបន្ទះ SiC ត្រូវបានផលិតយ៉ាងដូចម្តេច?

ក:

បន្ទះ SiC ផលិតជំហានលម្អិត

-

បន្ទះ SiCការរៀបចំវត្ថុធាតុដើម

- ប្រើម្សៅ SiC ថ្នាក់ ≥5N (ភាពមិនបរិសុទ្ធ ≤1 ppm)។

- ច្រោះហើយដុតជាមុនដើម្បីយកសមាសធាតុកាបូន ឬអាសូតដែលនៅសេសសល់ចេញ។

-

ស៊ីស៊ីការរៀបចំគ្រីស្តាល់គ្រាប់ពូជ

-

យកបំណែកគ្រីស្តាល់ទោល 4H-SiC មួយដុំ កាត់តាមទិសដៅ 〈0001〉 ដល់ ~10 × 10 mm²។

-

ប៉ូលាយ៉ាងម៉ត់ចត់ដល់ Ra ≤0.1 nm និងសម្គាល់ទិសដៅគ្រីស្តាល់។

-

-

ស៊ីស៊ីការលូតលាស់ PVT (ការដឹកជញ្ជូនចំហាយទឹករូបវន្ត)

-

ផ្ទុកចង្ក្រានក្រាហ្វីត៖ ដាក់ម្សៅ SiC នៅបាត និងដាក់គ្រីស្តាល់គ្រាប់នៅពីលើ។

-

បង្ហូរឧស្ម័នទៅដល់ 10⁻³–10⁻⁵ Torr ឬបំពេញជាមួយអេលីយ៉ូមបរិសុទ្ធខ្ពស់នៅសម្ពាធ 1 atm។

-

តំបន់ប្រភពកំដៅដល់ 2100–2300 ℃ រក្សាតំបន់គ្រាប់ពូជឱ្យត្រជាក់ជាង 100–150 ℃។

-

គ្រប់គ្រងអត្រាលូតលាស់នៅ 1–5 មីលីម៉ែត្រ/ម៉ោង ដើម្បីធ្វើឱ្យគុណភាព និងទិន្នផលមានតុល្យភាព។

-

-

ស៊ីស៊ីការដុតដែកអ៊ីណុក

-

ដុតដុំ SiC ដែលបានដាំរួចនៅសីតុណ្ហភាព 1600–1800 ℃ រយៈពេល 4–8 ម៉ោង។

-

គោលបំណង៖ បំបាត់ភាពតានតឹងកម្ដៅ និងកាត់បន្ថយដង់ស៊ីតេនៃការផ្លាស់ទីលំនៅ។

-

-

ស៊ីស៊ីការកាត់បន្ទះស្តើងៗ

-

ប្រើកាំបិតកាត់លួសពេជ្រ ដើម្បីកាត់ដុំដែកជាបន្ទះស្តើងកម្រាស់ 0.5–1 ម.ម។

-

កាត់បន្ថយរំញ័រ និងកម្លាំងពីចំហៀង ដើម្បីជៀសវាងការប្រេះតូចៗ។

-

-

ស៊ីស៊ីនំវ៉ាហ្វើរការកិន និង ការប៉ូលា

-

ការកិនរដុបដើម្បីលុបបំបាត់ការខូចខាតដោយសារការកាត់ (ភាពរដុប ~10–30 µm)។

-

ការកិនល្អិតល្អន់ដើម្បីសម្រេចបានភាពរាបស្មើ ≤5 µm។

-

ការប៉ូលាគីមី-មេកានិច (CMP)ដើម្បីសម្រេចបាននូវផ្ទៃរលោងដូចកញ្ចក់ (Ra ≤0.2 nm)។

-

-

ស៊ីស៊ីនំវ៉ាហ្វើរការសម្អាត និងការត្រួតពិនិត្យ

-

ការសម្អាតដោយអ៊ុលត្រាសោននៅក្នុងដំណោះស្រាយ Piranha (H₂SO₄:H₂O₂), ទឹក DI, បន្ទាប់មក IPA ។

-

វិសាលគម XRD/រ៉ាម៉ានដើម្បីបញ្ជាក់ពីពហុប្រភេទ (4H, 6H, 3C)។

-

អន្តរកម្មដើម្បីវាស់ភាពសំប៉ែត (<5 µm) និងរួញ (<20 µm)។

-

ការស៊ើបអង្កេតបួនចំណុចដើម្បីសាកល្បងភាពធន់ (ឧទាហរណ៍ HPSI ≥10⁹ Ω·cm)។

-

ការត្រួតពិនិត្យកំហុសមីក្រូទស្សន៍ក្រោមពន្លឺប៉ូល និងឧបករណ៍សាកល្បងកោស។

-

-

ស៊ីស៊ីនំវ៉ាហ្វើរការចាត់ថ្នាក់ និងការតម្រៀប

-

តម្រៀបបន្ទះសៀគ្វីតាមប្រភេទប៉ូលីទីប និងប្រភេទអគ្គិសនី៖

-

ប្រភេទ N-SiC 4H (4H-N): កំហាប់សារធាតុផ្ទុក 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC ភាពបរិសុទ្ធខ្ពស់ពាក់កណ្តាលអ៊ីសូឡង់ (4H-HPSI): ភាពធន់ ≥10⁹ Ω·សង់ទីម៉ែត្រ

-

ប្រភេទ N-6H-SiC (6H-N)

-

ផ្សេងៗ៖ 3C-SiC, ប្រភេទ P ជាដើម។

-

-

-

ស៊ីស៊ីនំវ៉ាហ្វើរការវេចខ្ចប់ និងការដឹកជញ្ជូន

2. សំណួរ៖ តើអ្វីទៅជាគុណសម្បត្តិសំខាន់ៗនៃបន្ទះស៊ីលីកុនលើបន្ទះស៊ីលីកុន?

ក: បើប្រៀបធៀបទៅនឹងបន្ទះស៊ីលីកុន បន្ទះ SiC អាចឱ្យ៖

-

ប្រតិបត្តិការវ៉ុលខ្ពស់(>1,200 V) ជាមួយនឹងភាពធន់នៃចរន្តអគ្គិសនីទាបជាង។

-

ស្ថេរភាពសីតុណ្ហភាពខ្ពស់ជាង(>300 °C) និងការគ្រប់គ្រងកម្ដៅបានប្រសើរឡើង។

-

ល្បឿនប្តូរលឿនជាងមុនជាមួយនឹងការខាតបង់ប្តូរទាប កាត់បន្ថយការត្រជាក់កម្រិតប្រព័ន្ធ និងទំហំនៅក្នុងឧបករណ៍បម្លែងថាមពល។

៤. សំណួរ៖ តើមានបញ្ហាអ្វីខ្លះដែលប៉ះពាល់ដល់ទិន្នផល និងដំណើរការបន្ទះស៊ីម៉ងត៍ SiC?

ក: ពិការភាពចម្បងនៅក្នុងបន្ទះ SiC រួមមាន បំពង់តូចៗ ការផ្លាស់ទីតាំងប្លង់មូលដ្ឋាន (BPDs) និងការកោសផ្ទៃ។ បំពង់តូចៗអាចបណ្តាលឱ្យខូចឧបករណ៍យ៉ាងធ្ងន់ធ្ងរ។ BPDs បង្កើនភាពធន់តាមពេលវេលា។ ហើយការកោសផ្ទៃនាំឱ្យមានការបាក់បន្ទះ wafer ឬការលូតលាស់ epitaxial មិនល្អ។ ដូច្នេះការត្រួតពិនិត្យយ៉ាងម៉ត់ចត់ និងការកាត់បន្ថយពិការភាពគឺមានសារៈសំខាន់ដើម្បីបង្កើនទិន្នផលបន្ទះ SiC ឱ្យបានអតិបរមា។

ពេលវេលាបង្ហោះ៖ ថ្ងៃទី 30 ខែមិថុនា ឆ្នាំ 2025