នៅក្នុងដំណើរការអភិវឌ្ឍន៍ដ៏រីកចម្រើននៃឧស្សាហកម្មស៊ីមីកុងដុកទ័រ គ្រីស្តាល់តែមួយដែលប៉ូលាបន្ទះស៊ីលីកុនដើរតួនាទីយ៉ាងសំខាន់។ ពួកវាបម្រើជាសម្ភារៈមូលដ្ឋានសម្រាប់ផលិតឧបករណ៍មីក្រូអេឡិចត្រូនិចផ្សេងៗ។ ចាប់ពីសៀគ្វីរួមបញ្ចូលគ្នាដ៏ស្មុគស្មាញ និងច្បាស់លាស់ រហូតដល់មីក្រូដំណើរការល្បឿនលឿន និងឧបករណ៍ចាប់សញ្ញាពហុមុខងារ គ្រីស្តាល់តែមួយដែលប៉ូលាបន្ទះស៊ីលីកុនគឺមានសារៈសំខាន់ណាស់។ ភាពខុសគ្នានៃដំណើរការ និងលក្ខណៈបច្ចេកទេសរបស់វាប៉ះពាល់ដោយផ្ទាល់ទៅលើគុណភាព និងដំណើរការនៃផលិតផលចុងក្រោយ។ ខាងក្រោមនេះគឺជាលក្ខណៈបច្ចេកទេស និងប៉ារ៉ាម៉ែត្រទូទៅនៃបន្ទះស៊ីលីកុនគ្រីស្តាល់តែមួយដែលប៉ូលា៖

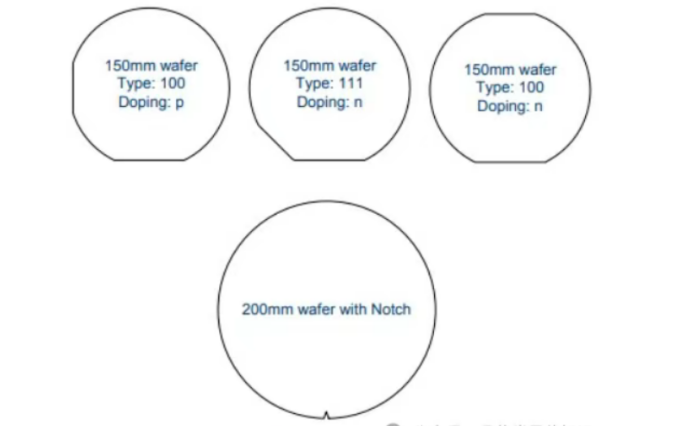

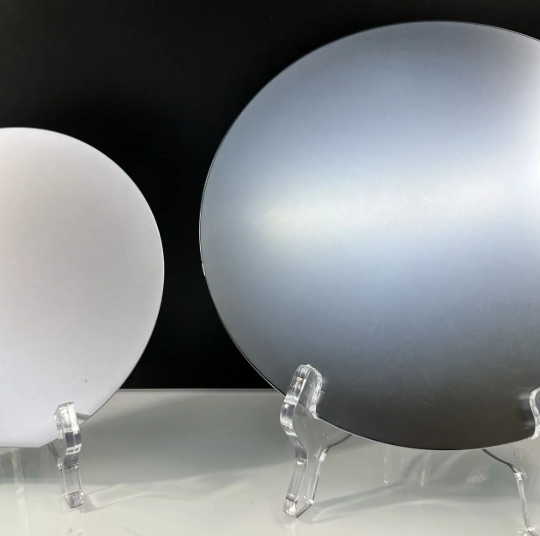

អង្កត់ផ្ចិត៖ ទំហំនៃបន្ទះស៊ីលីកុនគ្រីស្តាល់តែមួយ semiconductor ត្រូវបានវាស់ដោយអង្កត់ផ្ចិតរបស់វា ហើយវាមានលក្ខណៈបច្ចេកទេសជាច្រើន។ អង្កត់ផ្ចិតទូទៅរួមមាន 2 អ៊ីញ (50.8mm), 3 អ៊ីញ (76.2mm), 4 អ៊ីញ (100mm), 5 អ៊ីញ (125mm), 6 អ៊ីញ (150mm), 8 អ៊ីញ (200mm), 12 អ៊ីញ (300mm) និង 18 អ៊ីញ (450mm)។ អង្កត់ផ្ចិតផ្សេងៗគ្នាគឺសមស្របសម្រាប់តម្រូវការផលិតកម្ម និងតម្រូវការដំណើរការផ្សេងៗ។ ឧទាហរណ៍ បន្ទះស៊ីលីកុនដែលមានអង្កត់ផ្ចិតតូចជាងត្រូវបានគេប្រើជាទូទៅសម្រាប់ឧបករណ៍មីក្រូអេឡិចត្រូនិចពិសេសដែលមានបរិមាណតិច ខណៈពេលដែលបន្ទះស៊ីលីកុនដែលមានអង្កត់ផ្ចិតធំជាងបង្ហាញពីប្រសិទ្ធភាពផលិតកម្មខ្ពស់ និងគុណសម្បត្តិចំណាយក្នុងការផលិតសៀគ្វីរួមបញ្ចូលគ្នាទ្រង់ទ្រាយធំ។ តម្រូវការផ្ទៃត្រូវបានចាត់ថ្នាក់ជាបន្ទះប៉ូលាម្ខាង (SSP) និងបន្ទះប៉ូលាម្ខាង (DSP)។ បន្ទះស៊ីលីកុនដែលមានប៉ូលាម្ខាងត្រូវបានប្រើសម្រាប់ឧបករណ៍ដែលត្រូវការភាពរាបស្មើខ្ពស់នៅម្ខាង ដូចជាឧបករណ៍ចាប់សញ្ញាមួយចំនួន។ បន្ទះស៊ីលីកុនដែលមានប៉ូលាម្ខាងត្រូវបានប្រើជាទូទៅសម្រាប់សៀគ្វីរួមបញ្ចូលគ្នា និងផលិតផលផ្សេងទៀតដែលត្រូវការភាពជាក់លាក់ខ្ពស់លើផ្ទៃទាំងពីរ។ តម្រូវការផ្ទៃ (បញ្ចប់): SSP ប៉ូលាម្ខាង / DSP ប៉ូលាទ្វេ។

ប្រភេទ/សារធាតុបន្ថែម៖ (1) ឧបករណ៍អេឡិចត្រូនិកប្រភេទ N៖ នៅពេលដែលអាតូមមិនបរិសុទ្ធមួយចំនួនត្រូវបានបញ្ចូលទៅក្នុងឧបករណ៍អេឡិចត្រូនិកខាងក្នុង ពួកវាផ្លាស់ប្តូរចរន្តអគ្គិសនីរបស់វា។ ឧទាហរណ៍ នៅពេលដែលធាតុប្រាំវ៉ាឡង់ដូចជាអាសូត (N) ផូស្វ័រ (P) អាសេនិច (As) ឬអង់ទីម៉ូនី (Sb) ត្រូវបានបន្ថែម អេឡិចត្រុងវ៉ាឡង់របស់ពួកវាបង្កើតជាចំណងកូវ៉ាឡង់ជាមួយអេឡិចត្រុងវ៉ាឡង់នៃអាតូមស៊ីលីកុនជុំវិញ ដោយបន្សល់ទុកអេឡិចត្រុងបន្ថែមមួយដែលមិនត្រូវបានចងដោយចំណងកូវ៉ាឡង់។ នេះបណ្តាលឱ្យមានកំហាប់អេឡិចត្រុងធំជាងកំហាប់រន្ធ ដែលបង្កើតជាឧបករណ៍អេឡិចត្រូនិកប្រភេទ N ដែលត្រូវបានគេស្គាល់ផងដែរថាជាឧបករណ៍អេឡិចត្រូនិកប្រភេទអេឡិចត្រុង។ ឧបករណ៍អេឡិចត្រូនិកប្រភេទ N គឺមានសារៈសំខាន់ក្នុងការផលិតឧបករណ៍ដែលត្រូវការអេឡិចត្រុងជាឧបករណ៍ផ្ទុកបន្ទុកសំខាន់ ដូចជាឧបករណ៍ថាមពលមួយចំនួន។ (2) ឧបករណ៍អេឡិចត្រូនិកប្រភេទ P៖ នៅពេលដែលធាតុមិនបរិសុទ្ធត្រីវ៉ាឡង់ដូចជាបូរ៉ុន (B) ហ្គាលីញ៉ូម (Ga) ឬអ៊ីនដ្យូម (In) ត្រូវបានបញ្ចូលទៅក្នុងឧបករណ៍អេឡិចត្រូនិកស៊ីលីកុន អេឡិចត្រុងវ៉ាឡង់នៃអាតូមមិនបរិសុទ្ធបង្កើតជាចំណងកូវ៉ាឡង់ជាមួយអាតូមស៊ីលីកុនជុំវិញ ប៉ុន្តែពួកវាខ្វះអេឡិចត្រុងវ៉ាឡង់យ៉ាងហោចណាស់មួយ ហើយមិនអាចបង្កើតជាចំណងកូវ៉ាឡង់ពេញលេញបានទេ។ នេះនាំឱ្យមានកំហាប់រន្ធធំជាងកំហាប់អេឡិចត្រុង ដែលបង្កើតជាស៊ីមីកុងដុកទ័រប្រភេទ P ដែលត្រូវបានគេស្គាល់ផងដែរថាជាស៊ីមីកុងដុកទ័រប្រភេទរន្ធ។ ស៊ីមីកុងដុកទ័រប្រភេទ P ដើរតួនាទីយ៉ាងសំខាន់ក្នុងការផលិតឧបករណ៍ដែលរន្ធបម្រើជាឧបករណ៍ផ្ទុកបន្ទុកសំខាន់ៗ ដូចជាឌីយ៉ូដ និងត្រង់ស៊ីស្ទ័រមួយចំនួន។

ភាពធន់៖ ភាពធន់គឺជាបរិមាណរូបវន្តសំខាន់ដែលវាស់ស្ទង់ចរន្តអគ្គិសនីនៃបន្ទះស៊ីលីកុនគ្រីស្តាល់តែមួយដែលប៉ូលា។ តម្លៃរបស់វាឆ្លុះបញ្ចាំងពីដំណើរការចរន្តរបស់សម្ភារៈ។ ភាពធន់កាន់តែទាប ភាពធន់នៃបន្ទះស៊ីលីកុនកាន់តែល្អ។ ផ្ទុយទៅវិញ ភាពធន់កាន់តែខ្ពស់ ភាពធន់កាន់តែអន់។ ភាពធន់នៃបន្ទះស៊ីលីកុនត្រូវបានកំណត់ដោយលក្ខណៈសម្បត្តិសម្ភារៈដែលមាននៅក្នុងខ្លួនរបស់វា ហើយសីតុណ្ហភាពក៏មានផលប៉ះពាល់គួរឱ្យកត់សម្គាល់ផងដែរ។ ជាទូទៅ ភាពធន់នៃបន្ទះស៊ីលីកុនកើនឡើងតាមសីតុណ្ហភាព។ ក្នុងការអនុវត្តជាក់ស្តែង ឧបករណ៍មីក្រូអេឡិចត្រូនិចផ្សេងៗគ្នាមានតម្រូវការភាពធន់ខុសៗគ្នាសម្រាប់បន្ទះស៊ីលីកុន។ ឧទាហរណ៍ បន្ទះស៊ីលីកុនដែលប្រើក្នុងការផលិតសៀគ្វីរួមបញ្ចូលគ្នាត្រូវការការគ្រប់គ្រងភាពធន់យ៉ាងច្បាស់លាស់ដើម្បីធានាបាននូវដំណើរការឧបករណ៍ដែលមានស្ថេរភាព និងអាចទុកចិត្តបាន។

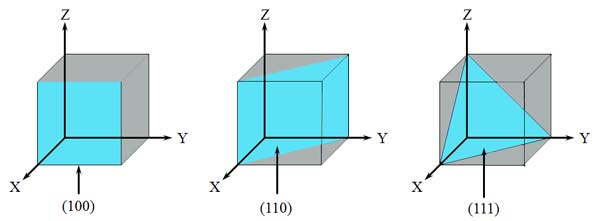

ទិសដៅ៖ ទិសដៅគ្រីស្តាល់នៃបន្ទះសៀគ្វីតំណាងឱ្យទិសដៅគ្រីស្តាល់នៃបន្ទះសៀគ្វីស៊ីលីកុន ដែលជាធម្មតាត្រូវបានបញ្ជាក់ដោយសន្ទស្សន៍មីលលើរដូចជា (100), (110), (111) ជាដើម។ ទិសដៅគ្រីស្តាល់ផ្សេងៗគ្នាមានលក្ខណៈសម្បត្តិរូបវន្តខុសៗគ្នា ដូចជាដង់ស៊ីតេបន្ទាត់ ដែលប្រែប្រួលអាស្រ័យលើទិសដៅ។ ភាពខុសគ្នានេះអាចប៉ះពាល់ដល់ដំណើរការរបស់បន្ទះសៀគ្វីនៅក្នុងជំហានដំណើរការជាបន្តបន្ទាប់ និងដំណើរការចុងក្រោយនៃឧបករណ៍មីក្រូអេឡិចត្រូនិច។ នៅក្នុងដំណើរការផលិត ការជ្រើសរើសបន្ទះសៀគ្វីស៊ីលីកុនដែលមានទិសដៅសមស្របសម្រាប់តម្រូវការឧបករណ៍ផ្សេងៗគ្នាអាចបង្កើនប្រសិទ្ធភាពដំណើរការឧបករណ៍ បង្កើនប្រសិទ្ធភាពផលិតកម្ម និងបង្កើនគុណភាពផលិតផល។

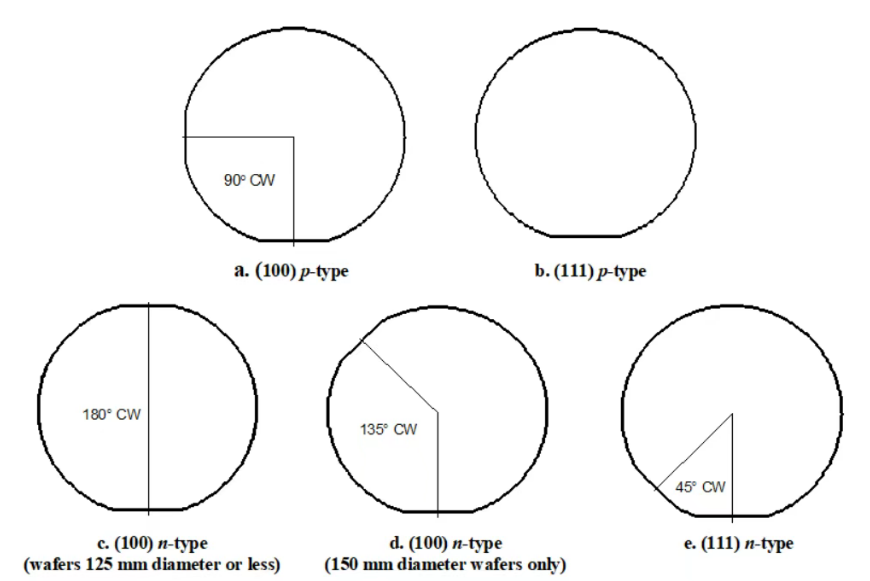

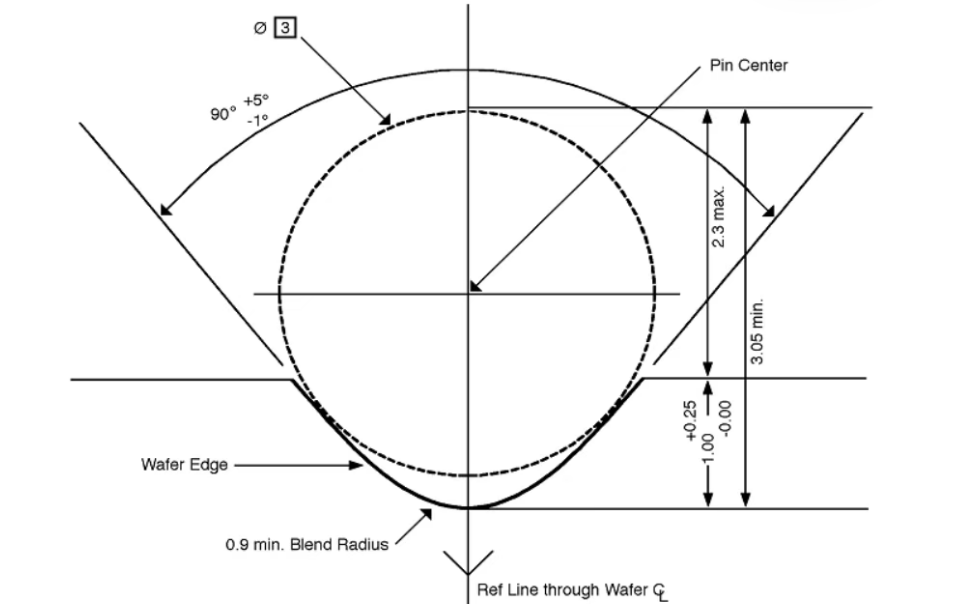

រាបស្មើ/ស្នាមរន្ធ៖ គែមរាបស្មើ (រាបស្មើ) ឬស្នាមរន្ធរាងអក្សរ V (ស្នាមរន្ធ) នៅលើបរិមាត្រនៃបន្ទះស៊ីលីកុនដើរតួនាទីយ៉ាងសំខាន់ក្នុងការតម្រឹមទិសដៅគ្រីស្តាល់ និងជាឧបករណ៍កំណត់អត្តសញ្ញាណសំខាន់ក្នុងការផលិត និងដំណើរការបន្ទះស៊ីលីកុន។ បន្ទះស៊ីលីកុនដែលមានអង្កត់ផ្ចិតខុសៗគ្នាត្រូវគ្នាទៅនឹងស្តង់ដារផ្សេងៗគ្នាសម្រាប់ប្រវែងបន្ទះស៊ីលីកុន ឬស្នាមរន្ធ។ គែមតម្រឹមត្រូវបានចាត់ថ្នាក់ជាបន្ទះស៊ីលីកុនបឋម និងបន្ទះស៊ីលីកុនបន្ទាប់បន្សំ។ បន្ទះស៊ីលីកុនបឋមត្រូវបានប្រើជាចម្បងដើម្បីកំណត់ទិសដៅគ្រីស្តាល់មូលដ្ឋាន និងឯកសារយោងដំណើរការនៃបន្ទះស៊ីលីកុន ខណៈពេលដែលបន្ទះស៊ីលីកុនបន្ទាប់បន្សំជួយបន្ថែមទៀតក្នុងការតម្រឹម និងដំណើរការយ៉ាងច្បាស់លាស់ ដែលធានាបាននូវប្រតិបត្តិការ និងភាពស៊ីសង្វាក់គ្នាត្រឹមត្រូវនៃបន្ទះស៊ីលីកុនពេញមួយខ្សែសង្វាក់ផលិតកម្ម។

កម្រាស់៖ កម្រាស់របស់បន្ទះសៀគ្វីជាធម្មតាត្រូវបានបញ្ជាក់ជាមីក្រូម៉ែត្រ (μm) ដែលមានកម្រាស់ទូទៅចន្លោះពី 100μm ដល់ 1000μm។ បន្ទះសៀគ្វីដែលមានកម្រាស់ខុសៗគ្នាគឺសមរម្យសម្រាប់ឧបករណ៍មីក្រូអេឡិចត្រូនិចប្រភេទផ្សេងៗគ្នា។ បន្ទះសៀគ្វីស្តើងជាង (ឧទាហរណ៍ 100μm – 300μm) ជារឿយៗត្រូវបានប្រើសម្រាប់ការផលិតបន្ទះឈីបដែលត្រូវការការគ្រប់គ្រងកម្រាស់យ៉ាងតឹងរ៉ឹង ដោយកាត់បន្ថយទំហំ និងទម្ងន់របស់បន្ទះឈីប និងបង្កើនដង់ស៊ីតេនៃការរួមបញ្ចូល។ បន្ទះសៀគ្វីក្រាស់ជាង (ឧទាហរណ៍ 500μm – 1000μm) ត្រូវបានគេប្រើប្រាស់យ៉ាងទូលំទូលាយនៅក្នុងឧបករណ៍ដែលត្រូវការកម្លាំងមេកានិចខ្ពស់ជាង ដូចជាឧបករណ៍អេឡិចត្រូនិចថាមពល ដើម្បីធានាបាននូវស្ថេរភាពក្នុងអំឡុងពេលប្រតិបត្តិការ។

ភាពរដុបនៃផ្ទៃ៖ ភាពរដុបនៃផ្ទៃគឺជាប៉ារ៉ាម៉ែត្រសំខាន់មួយសម្រាប់វាយតម្លៃគុណភាពបន្ទះសៀគ្វី ព្រោះវាប៉ះពាល់ដោយផ្ទាល់ទៅលើភាពស្អិតរវាងបន្ទះសៀគ្វី និងសម្ភារៈខ្សែភាពយន្តស្តើងដែលបានដាក់ជាបន្តបន្ទាប់ ក៏ដូចជាដំណើរការអគ្គិសនីរបស់ឧបករណ៍។ ជាធម្មតាវាត្រូវបានបង្ហាញជាភាពរដុបនៃមធ្យមការ៉េ (RMS) (គិតជា nm)។ ភាពរដុបនៃផ្ទៃទាបមានន័យថាផ្ទៃបន្ទះសៀគ្វីរលោងជាងមុន ដែលជួយកាត់បន្ថយបាតុភូតដូចជាការខ្ចាត់ខ្ចាយអេឡិចត្រុង និងធ្វើអោយប្រសើរឡើងនូវដំណើរការ និងភាពជឿជាក់របស់ឧបករណ៍។ នៅក្នុងដំណើរការផលិតឧបករណ៍អេឡិចត្រូនិកកម្រិតខ្ពស់ តម្រូវការរដុបនៃផ្ទៃកាន់តែតឹងរ៉ឹង ជាពិសេសសម្រាប់ការផលិតសៀគ្វីរួមបញ្ចូលគ្នាកម្រិតខ្ពស់ ដែលភាពរដុបនៃផ្ទៃត្រូវតែគ្រប់គ្រងទៅពីរបីណាណូម៉ែត្រ ឬទាបជាងនេះ។

ការប្រែប្រួលកម្រាស់សរុប (TTV): ការប្រែប្រួលកម្រាស់សរុបសំដៅទៅលើភាពខុសគ្នារវាងកម្រាស់អតិបរមា និងអប្បបរមាដែលវាស់នៅចំណុចច្រើននៅលើផ្ទៃបន្ទះសៀគ្វី ដែលជាធម្មតាត្រូវបានបង្ហាញជា μm។ TTV ខ្ពស់អាចនាំឱ្យមានគម្លាតនៅក្នុងដំណើរការដូចជាការថតចម្លងពន្លឺ និងការឆ្លាក់ ដែលប៉ះពាល់ដល់ភាពស៊ីសង្វាក់គ្នានៃដំណើរការឧបករណ៍ និងទិន្នផល។ ដូច្នេះ ការគ្រប់គ្រង TTV ក្នុងអំឡុងពេលផលិតបន្ទះសៀគ្វីគឺជាជំហានសំខាន់ក្នុងការធានាគុណភាពផលិតផល។ សម្រាប់ការផលិតឧបករណ៍មីក្រូអេឡិចត្រូនិចដែលមានភាពជាក់លាក់ខ្ពស់ TTV ជាធម្មតាត្រូវបានទាមទារឱ្យស្ថិតនៅក្នុងចម្ងាយពីរបីមីក្រូម៉ែត្រ។

កោង៖ កោងសំដៅលើគម្លាតរវាងផ្ទៃបន្ទះសៀគ្វី និងប្លង់រាបស្មើដ៏ល្អ ដែលជាធម្មតាត្រូវបានវាស់វែងជា μm។ បន្ទះសៀគ្វីដែលមានកោងខ្លាំងពេកអាចបាក់ ឬជួបប្រទះភាពតានតឹងមិនស្មើគ្នាក្នុងអំឡុងពេលដំណើរការជាបន្តបន្ទាប់ ដែលប៉ះពាល់ដល់ប្រសិទ្ធភាពផលិតកម្ម និងគុណភាពផលិតផល។ ជាពិសេសនៅក្នុងដំណើរការដែលត្រូវការភាពរាបស្មើខ្ពស់ ដូចជាការថតចម្លងដោយពន្លឺ ការកោងត្រូវតែគ្រប់គ្រងក្នុងចន្លោះជាក់លាក់មួយ ដើម្បីធានាបាននូវភាពត្រឹមត្រូវ និងភាពស៊ីសង្វាក់គ្នានៃលំនាំថតចម្លងដោយពន្លឺ។

ការរួញ៖ ការរួញបង្ហាញពីគម្លាតរវាងផ្ទៃបន្ទះសៀគ្វី និងរាងស្វ៊ែរដ៏ល្អ ដែលវាស់វែងជា μm ផងដែរ។ ស្រដៀងគ្នាទៅនឹងរាងកោង ការរួញគឺជាសូចនាករសំខាន់មួយនៃភាពសំប៉ែតបន្ទះសៀគ្វី។ ការរួញហួសប្រមាណមិនត្រឹមតែប៉ះពាល់ដល់ភាពត្រឹមត្រូវនៃការដាក់បន្ទះសៀគ្វីនៅក្នុងឧបករណ៍ដំណើរការប៉ុណ្ណោះទេ ប៉ុន្តែថែមទាំងអាចបង្កបញ្ហាក្នុងអំឡុងពេលដំណើរការវេចខ្ចប់បន្ទះឈីបផងដែរ ដូចជាការភ្ជាប់មិនល្អរវាងបន្ទះឈីប និងសម្ភារៈវេចខ្ចប់ ដែលវាប៉ះពាល់ដល់ភាពជឿជាក់នៃឧបករណ៍។ នៅក្នុងការផលិតឧបករណ៍អេឡិចត្រូនិកកម្រិតខ្ពស់ តម្រូវការរួញកាន់តែតឹងរ៉ឹងដើម្បីបំពេញតម្រូវការនៃដំណើរការផលិតបន្ទះឈីបកម្រិតខ្ពស់ និងដំណើរការវេចខ្ចប់។

ទម្រង់គែម៖ ទម្រង់គែមរបស់បន្ទះសៀគ្វីគឺមានសារៈសំខាន់សម្រាប់ដំណើរការ និងការគ្រប់គ្រងជាបន្តបន្ទាប់របស់វា។ ជាធម្មតាវាត្រូវបានបញ្ជាក់ដោយតំបន់ដកចេញគែម (EEZ) ដែលកំណត់ចម្ងាយពីគែមបន្ទះសៀគ្វីដែលមិនអនុញ្ញាតឱ្យមានដំណើរការ។ ទម្រង់គែមដែលត្រូវបានរចនាយ៉ាងត្រឹមត្រូវ និងការគ្រប់គ្រង EEZ ដ៏ច្បាស់លាស់ជួយជៀសវាងពិការភាពគែម កំហាប់ភាពតានតឹង និងបញ្ហាផ្សេងទៀតក្នុងអំឡុងពេលដំណើរការ ដែលធ្វើអោយប្រសើរឡើងនូវគុណភាព និងទិន្នផលបន្ទះសៀគ្វីទាំងមូល។ នៅក្នុងដំណើរការផលិតកម្រិតខ្ពស់មួយចំនួន ភាពជាក់លាក់នៃទម្រង់គែមត្រូវបានទាមទារឱ្យនៅកម្រិតមីក្រូរង។

ចំនួនភាគល្អិត៖ ការចែកចាយចំនួន និងទំហំនៃភាគល្អិតនៅលើផ្ទៃបន្ទះសៀគ្វីប៉ះពាល់យ៉ាងខ្លាំងដល់ដំណើរការនៃឧបករណ៍មីក្រូអេឡិចត្រូនិច។ ភាគល្អិតលើស ឬធំអាចនាំឱ្យមានការបរាជ័យនៃឧបករណ៍ ដូចជាសៀគ្វីខ្លី ឬការលេចធ្លាយ ដែលកាត់បន្ថយទិន្នផលផលិតផល។ ដូច្នេះ ចំនួនភាគល្អិតជាធម្មតាត្រូវបានវាស់វែងដោយការរាប់ភាគល្អិតក្នុងមួយឯកតាផ្ទៃ ដូចជាចំនួនភាគល្អិតធំជាង 0.3 μm។ ការគ្រប់គ្រងយ៉ាងតឹងរ៉ឹងនៃចំនួនភាគល្អិតក្នុងអំឡុងពេលផលិតបន្ទះសៀគ្វីគឺជាវិធានការសំខាន់សម្រាប់ធានាគុណភាពផលិតផល។ បច្ចេកវិទ្យាសម្អាតកម្រិតខ្ពស់ និងបរិយាកាសផលិតកម្មស្អាតត្រូវបានប្រើដើម្បីកាត់បន្ថយការចម្លងរោគភាគល្អិតនៅលើផ្ទៃបន្ទះសៀគ្វី។

![]()

![]()

![]()

![]()

![]()

ផលិតកម្មពាក់ព័ន្ធ

បន្ទះស៊ីលីកុនគ្រីស្តាល់តែមួយ Si ប្រភេទស្រទាប់ខាងក្រោម N/P បន្ទះស៊ីលីកុនកាប៊ីតជាជម្រើស

បន្ទះស៊ីលីកុន FZ CZ Si មានស្តុក បន្ទះស៊ីលីកុនទំហំ 12 អ៊ីញ សម្រាប់សាកល្បង ឬ សាកល្បង

ពេលវេលាបង្ហោះ៖ ថ្ងៃទី ១៨ ខែមេសា ឆ្នាំ ២០២៥