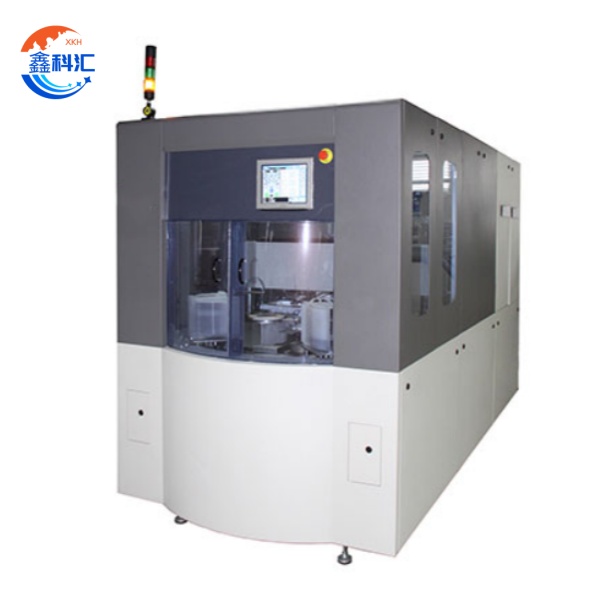

ឧបករណ៍ធ្វើឲ្យស្តើងបន្ទះស្តើងសម្រាប់ដំណើរការបន្ទះស្តើង Sapphire/SiC/Si ទំហំ 4 អ៊ីញ ដល់ 12 អ៊ីញ

គោលការណ៍ធ្វើការ

ដំណើរការនៃការធ្វើឱ្យស្តើង wafer ដំណើរការជាបីដំណាក់កាល៖

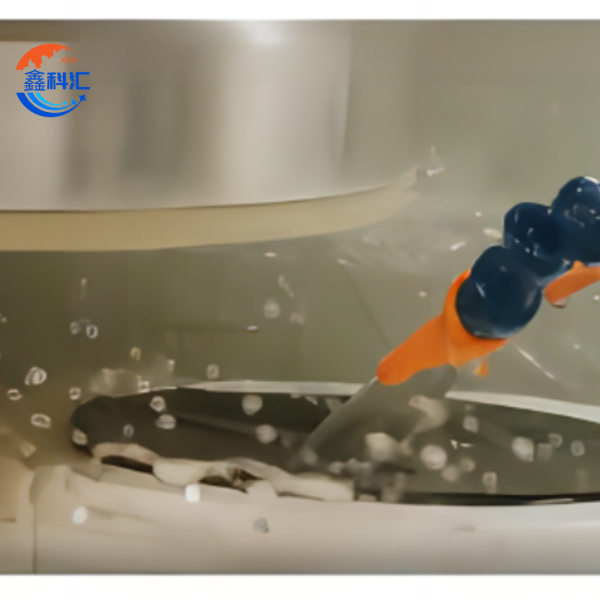

ការកិនរដុប៖ កង់ពេជ្រ (ទំហំគ្រាប់ធញ្ញជាតិ 200–500 μm) យកសម្ភារៈចំនួន 50–150 μm ចេញ ក្នុងល្បឿន 3000–5000 rpm ដើម្បីកាត់បន្ថយកម្រាស់យ៉ាងឆាប់រហ័ស។

ការកិនល្អិតៗ៖ កង់ល្អិតៗ (ទំហំគ្រាប់គ្រើម 1–50 μm) កាត់បន្ថយកម្រាស់មកត្រឹម 20–50 μm នៅកម្រិត <1 μm/s ដើម្បីកាត់បន្ថយការខូចខាតក្រោមផ្ទៃដី។

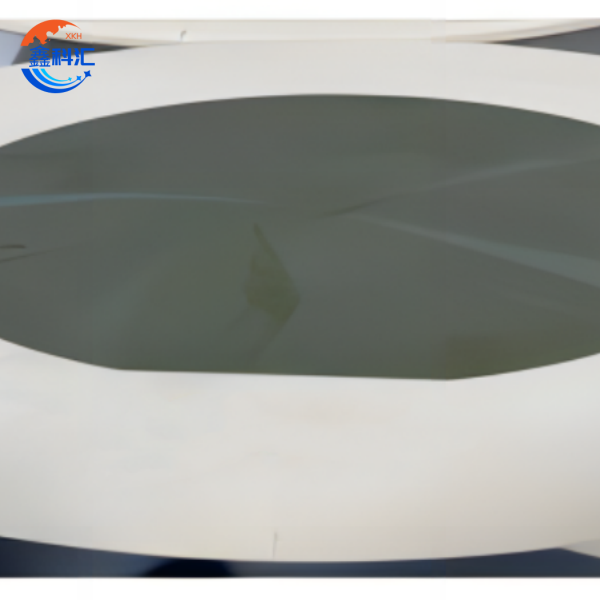

ការប៉ូលា (CMP): សារធាតុគីមី-មេកានិចលុបបំបាត់ការខូចខាតដែលនៅសេសសល់ ដោយសម្រេចបាន Ra < 0.1 nm។

សម្ភារៈដែលឆបគ្នា

ស៊ីលីកុន (Si): ស្តង់ដារសម្រាប់បន្ទះសៀគ្វី CMOS ស្តើងដល់ 25 μm សម្រាប់ការដាក់ជង់ 3D។

ស៊ីលីកុនកាបៃ (SiC): តម្រូវឱ្យមានកង់ពេជ្រឯកទេស (កំហាប់ពេជ្រ 80%) សម្រាប់ស្ថេរភាពកម្ដៅ។

ត្បូងកណ្តៀង (Al₂O₃): ស្តើងដល់ 50 μm សម្រាប់កម្មវិធី UV LED។

សមាសធាតុប្រព័ន្ធស្នូល

១. ប្រព័ន្ធកិន

ម៉ាស៊ីនកិនអ័ក្សពីរ៖ រួមបញ្ចូលគ្នានូវការកិនរដុប/ល្អិតៗក្នុងវេទិកាតែមួយ ដែលកាត់បន្ថយពេលវេលាវដ្តបាន 40%។

Aerostatic Spindle៖ ជួរល្បឿន ០–៦០០០ rpm ជាមួយនឹងការរត់ចេញជារ៉ាឌីកាល់ <០.៥ μm។

២. ប្រព័ន្ធដោះស្រាយបន្ទះស្តើង

ក្បាលវីសបូមធូលី៖ កម្លាំងកាន់ >50 N ជាមួយនឹងភាពត្រឹមត្រូវនៃទីតាំង ±0.1 μm។

ដៃរ៉ូបូត៖ ដឹកជញ្ជូនបន្ទះស្តើងទំហំ ៤-១២ អ៊ីញ ក្នុងល្បឿន ១០០ មីលីម៉ែត្រ/វិនាទី។

៣. ប្រព័ន្ធត្រួតពិនិត្យ

អន្តរកម្មឡាស៊ែរ៖ ការត្រួតពិនិត្យកម្រាស់ពេលវេលាជាក់ស្តែង (គុណភាពបង្ហាញ 0.01 μm)។

បច្ចេកវិទ្យា AI-Driven Feedforward៖ ព្យាករណ៍ពីការសឹករិចរិលរបស់កង់ និងកែតម្រូវប៉ារ៉ាម៉ែត្រដោយស្វ័យប្រវត្តិ។

៤. ម៉ាស៊ីនត្រជាក់ និងសម្អាត

ការសម្អាតដោយអ៊ុលត្រាសោន៖ យកភាគល្អិតចេញ >0.5 μm ជាមួយនឹងប្រសិទ្ធភាព 99.9%។

ទឹកគ្មានអ៊ីយ៉ុង៖ ធ្វើឱ្យនំវ៉ាហ្វើរត្រជាក់ដល់ <5°C ពីលើបរិយាកាស។

គុណសម្បត្តិស្នូល

១. ភាពជាក់លាក់ខ្ពស់បំផុត៖ TTV (ការប្រែប្រួលកម្រាស់សរុប) <០.៥ μm, WTW (ការប្រែប្រួលកម្រាស់ក្នុងបន្ទះ) <១ μm។

២. ការរួមបញ្ចូលដំណើរការច្រើន៖ រួមបញ្ចូលគ្នានូវការកិន ការកែច្នៃ CMP និងការឆ្លាក់ប្លាស្មានៅក្នុងម៉ាស៊ីនតែមួយ។

៣. ភាពឆបគ្នានៃសម្ភារៈ៖

ស៊ីលីកុន៖ ការកាត់បន្ថយកម្រាស់ពី 775 μm មកត្រឹម 25 μm។

SiC: សម្រេចបាន TTV <2 μm សម្រាប់កម្មវិធី RF។

បន្ទះវ៉ាហ្វឺរដែលមានជាតិផូស្វ័រ៖ បន្ទះវ៉ាហ្វឺរ InP ដែលមានជាតិផូស្វ័រ ដែលមានភាពរសាត់រេស៊ីស្តង់ <5%។

៤. ស្វ័យប្រវត្តិកម្មឆ្លាតវៃ៖ ការរួមបញ្ចូល MES កាត់បន្ថយកំហុសរបស់មនុស្សបាន ៧០%។

៥. ប្រសិទ្ធភាពថាមពល៖ ការប្រើប្រាស់ថាមពលទាបជាង 30% តាមរយៈការហ្វ្រាំងបង្កើតឡើងវិញ។

កម្មវិធីសំខាន់ៗ

១. ការវេចខ្ចប់កម្រិតខ្ពស់

• ICs 3D៖ ការស្តើងបន្ទះសៀគ្វី Wafer អនុញ្ញាតឱ្យដាក់ជង់បញ្ឈរនៃបន្ទះឈីបឡូជីខល/អង្គចងចាំ (ឧទាហរណ៍ ជង់ HBM) ដោយសម្រេចបាននូវកម្រិតបញ្ជូនខ្ពស់ជាង 10 ដង និងការប្រើប្រាស់ថាមពលតិចជាង 50% បើប្រៀបធៀបទៅនឹងដំណោះស្រាយ 2.5D។ ឧបករណ៍នេះគាំទ្រការភ្ជាប់កូនកាត់ និងការរួមបញ្ចូល TSV (Through-Silicon Via) ដែលមានសារៈសំខាន់សម្រាប់ប្រព័ន្ធដំណើរការ AI/ML ដែលត្រូវការចម្ងាយភ្ជាប់ <10 μm។ ឧទាហរណ៍ បន្ទះសៀគ្វី Wafer ទំហំ 12 អ៊ីញដែលត្រូវបានស្តើងដល់ 25 μm អនុញ្ញាតឱ្យដាក់ជង់ 8+ ស្រទាប់ ខណៈពេលដែលរក្សាបាននូវភាពរួញតូច <1.5% ដែលមានសារៈសំខាន់សម្រាប់ប្រព័ន្ធ LiDAR រថយន្ត។

• ការវេចខ្ចប់បែបកង្ហារ៖ តាមរយៈការកាត់បន្ថយកម្រាស់បន្ទះសៀគ្វីមកត្រឹម 30 μm ប្រវែងភ្ជាប់ត្រូវបានខ្លី 50% ដែលកាត់បន្ថយការពន្យាពេលសញ្ញា (<0.2 ps/mm) និងអាចឱ្យបន្ទះឈីបស្តើងបំផុត 0.4 mm សម្រាប់ SoC ចល័ត។ ដំណើរការនេះប្រើប្រាស់ក្បួនដោះស្រាយកិនដែលផ្តល់សំណងដោយភាពតានតឹងដើម្បីការពារការកោង (ការគ្រប់គ្រង TTV >50 μm) ដែលធានាបាននូវភាពជឿជាក់នៅក្នុងកម្មវិធី RF ប្រេកង់ខ្ពស់។

២. គ្រឿងអេឡិចត្រូនិចថាមពល

• ម៉ូឌុល IGBT៖ ការស្តើងដល់ 50 μm កាត់បន្ថយភាពធន់នឹងកម្ដៅដល់ <0.5°C/W ដែលអាចឱ្យ MOSFETs SiC 1200V ដំណើរការនៅសីតុណ្ហភាពប្រសព្វ 200°C។ ឧបករណ៍របស់យើងប្រើប្រាស់ការកិនច្រើនដំណាក់កាល (រដុប៖ ក្រួស 46 μm → ល្អិត៖ ក្រួស 4 μm) ដើម្បីលុបបំបាត់ការខូចខាតក្រោមផ្ទៃដី ដោយសម្រេចបាន >10,000 វដ្តនៃភាពជឿជាក់នៃវដ្តកម្ដៅ។ នេះគឺមានសារៈសំខាន់សម្រាប់អាំងវឺរទ័រ EV ដែលបន្ទះ SiC កម្រាស់ 10 μm ធ្វើអោយល្បឿនប្តូរប្រសើរឡើង 30%។

• ឧបករណ៍ថាមពល GaN-on-SiC៖ ការស្តើងបន្ទះសៀគ្វីដល់ 80 μm ជួយបង្កើនការចល័តអេឡិចត្រុង (μ > 2000 cm²/V·s) សម្រាប់ HEMTs GaN 650V ដោយកាត់បន្ថយការខាតបង់ចរន្តអគ្គិសនី 18%។ ដំណើរការនេះប្រើការកាត់ជាដុំៗដែលមានជំនួយពីឡាស៊ែរ ដើម្បីការពារការប្រេះអំឡុងពេលស្តើង ដោយសម្រេចបានការបំបែកគែម <5 μm សម្រាប់ឧបករណ៍ពង្រីកថាមពល RF។

៣. អុបតូអេឡិចត្រូនិច

• អំពូល LED GaN-on-SiC៖ ស្រទាប់ត្បូងកណ្តៀង 50 μm ធ្វើអោយប្រសើរឡើងនូវប្រសិទ្ធភាពទាញយកពន្លឺ (LEE) ដល់ 85% (ធៀបនឹង 65% សម្រាប់បន្ទះ ...

• ស៊ីលីកុនហ្វូតូនិក៖ បន្ទះស៊ីលីកុនកម្រាស់ 25μm អាចឱ្យការបាត់បង់ការសាយភាយទាបជាង 3 dB/cm2 នៅក្នុងរលកនាំផ្លូវ ដែលមានសារៈសំខាន់សម្រាប់ឧបករណ៍បញ្ជូនអុបទិក 1.6 Tbps។ ដំណើរការនេះរួមបញ្ចូលការធ្វើឱ្យរលោង CMP ដើម្បីកាត់បន្ថយភាពរដុបនៃផ្ទៃដល់ Ra <0.1 nm ដែលបង្កើនប្រសិទ្ធភាពភ្ជាប់ 40%។

៤. ឧបករណ៍ចាប់សញ្ញា MEMS

• ឧបករណ៍វាស់ល្បឿន៖ បន្ទះស៊ីលីកុនកម្រាស់ 25 μm សម្រេចបាន SNR >85 dB (ធៀបនឹង 75 dB សម្រាប់បន្ទះស៊ីលីកុនកម្រាស់ 50 μm) ដោយបង្កើនភាពរសើបនៃការផ្លាស់ទីលំនៅរបស់ម៉ាស់ភស្តុតាង។ ប្រព័ន្ធកិនអ័ក្សពីររបស់យើងផ្តល់សំណងសម្រាប់ជម្រាលភាពតានតឹង ដោយធានាបាននូវភាពរសើប <0.5% លើសពី -40°C ដល់ 125°C។ កម្មវិធីរួមមានការរកឃើញការប៉ះទង្គិចរថយន្ត និងការតាមដានចលនា AR/VR។

• ឧបករណ៍ចាប់សញ្ញាសម្ពាធ៖ ការស្តើងដល់ 40 μm អនុញ្ញាតឱ្យមានជួរវាស់ 0–300 បារ ជាមួយនឹង hysteresis FS <0.1%។ ដោយប្រើការភ្ជាប់បណ្តោះអាសន្ន (ឧបករណ៍ផ្ទុកកញ្ចក់) ដំណើរការនេះជៀសវាងការបាក់បន្ទះ wafer អំឡុងពេលឆ្លាក់ផ្នែកខាងក្រោយ ដោយសម្រេចបានការអត់ធ្មត់លើសសម្ពាធ <1 μm សម្រាប់ឧបករណ៍ចាប់សញ្ញា IoT ឧស្សាហកម្ម។

• សមាហរណកម្មបច្ចេកទេស៖ ឧបករណ៍ស្តើងបន្ទះស្តើងរបស់យើងបង្រួបបង្រួមការកិនមេកានិច CMP និងការឆ្លាក់ប្លាស្មា ដើម្បីដោះស្រាយបញ្ហាប្រឈមនៃសម្ភារៈចម្រុះ (Si, SiC, Sapphire)។ ឧទាហរណ៍ GaN-on-SiC តម្រូវឱ្យមានការកិនចម្រុះ (កង់ពេជ្រ + ប្លាស្មា) ដើម្បីធ្វើឱ្យមានតុល្យភាពរវាងភាពរឹង និងការពង្រីកកម្ដៅ ខណៈដែលឧបករណ៍ចាប់សញ្ញា MEMS ទាមទារភាពរដុបនៃផ្ទៃក្រោម 5 nm តាមរយៈការប៉ូលា CMP។

• ផលប៉ះពាល់ឧស្សាហកម្ម៖ តាមរយៈការបង្កើតបន្ទះសៀគ្វីស្តើងជាងមុន និងមានដំណើរការខ្ពស់ជាងមុន បច្ចេកវិទ្យានេះជំរុញការច្នៃប្រឌិតថ្មីនៅក្នុងបន្ទះឈីប AI ម៉ូឌុល 5G mmWave និងឧបករណ៍អេឡិចត្រូនិចដែលអាចបត់បែនបាន ជាមួយនឹងការអត់ធ្មត់ TTV <0.1 μm សម្រាប់អេក្រង់បត់បាន និង <0.5 μm សម្រាប់ឧបករណ៍ចាប់សញ្ញា LiDAR សម្រាប់រថយន្ត។

សេវាកម្មរបស់ XKH

១. ដំណោះស្រាយដែលបានកំណត់តាមតម្រូវការ

ការកំណត់រចនាសម្ព័ន្ធដែលអាចធ្វើមាត្រដ្ឋានបាន៖ ការរចនាបន្ទប់ទំហំ ៤-១២ អ៊ីញជាមួយនឹងការផ្ទុក/ផ្ទុកដោយស្វ័យប្រវត្តិ។

ការគាំទ្រការប្រើប្រាស់សារធាតុដូប៉ង់៖ រូបមន្តផ្ទាល់ខ្លួនសម្រាប់គ្រីស្តាល់ដែលមានដូប៉ង់ Er/Yb និងបន្ទះ InP/GaAs។

២. ការគាំទ្រពីដើមដល់ចប់

ការអភិវឌ្ឍដំណើរការ៖ ការសាកល្បងឥតគិតថ្លៃដំណើរការជាមួយនឹងការបង្កើនប្រសិទ្ធភាព។

ការបណ្តុះបណ្តាលសកល៖ សិក្ខាសាលាបច្ចេកទេសជារៀងរាល់ឆ្នាំលើការថែទាំ និងការដោះស្រាយបញ្ហា។

៣. ដំណើរការពហុសម្ភារៈ

SiC: បន្ទះស្តើងដល់ 100 μm ជាមួយ Ra < 0.1 nm។

ត្បូងកណ្តៀង៖ កម្រាស់ 50μm សម្រាប់បង្អួចឡាស៊ែរ UV (ការបញ្ជូន >92%@200 nm)។

៤. សេវាកម្មបន្ថែមតម្លៃ

ការផ្គត់ផ្គង់សម្រាប់ប្រើប្រាស់៖ កង់ពេជ្រ (បន្ទះស្តើងៗចំនួន 2000+ បន្ទះ/ជីវិត) និងសារធាតុស្អិត CMP។

សេចក្តីសន្និដ្ឋាន

ឧបករណ៍ស្តើងបន្ទះស្តើងនេះផ្តល់នូវភាពជាក់លាក់ឈានមុខគេក្នុងឧស្សាហកម្ម ភាពបត់បែននៃសម្ភារៈច្រើនប្រភេទ និងស្វ័យប្រវត្តិកម្មឆ្លាតវៃ ដែលធ្វើឱ្យវាមិនអាចខ្វះបានសម្រាប់ការរួមបញ្ចូល 3D និងអេឡិចត្រូនិចថាមពល។ សេវាកម្មដ៏ទូលំទូលាយរបស់ XKH — ចាប់ពីការប្ដូរតាមបំណងរហូតដល់ការកែច្នៃក្រោយ — ធានាថាអតិថិជនសម្រេចបានប្រសិទ្ធភាពចំណាយ និងឧត្តមភាពនៃការអនុវត្តក្នុងការផលិតស៊ីមីកុងដុកទ័រ។