បន្ទះសៀគ្វី SiC ទំហំ ៤ អ៊ីញ 6H ស្រទាប់ខាងក្រោម SiC ពាក់កណ្តាលអ៊ីសូឡង់ ជាថ្នាក់បឋម ថ្នាក់ស្រាវជ្រាវ និងថ្នាក់សាកល្បង

លក្ខណៈបច្ចេកទេសផលិតផល

| ថ្នាក់ | ថ្នាក់ផលិតកម្ម MPD សូន្យ (ថ្នាក់ Z) | ថ្នាក់ផលិតកម្មស្តង់ដារ (ថ្នាក់ P) | ថ្នាក់ D (ថ្នាក់ D) | ||||||||

| អង្កត់ផ្ចិត | ៩៩.៥ ម.ម. ~ ១០០.០ ម.ម. | ||||||||||

| 4H-SI | ៥០០ មីក្រូម៉ែត្រ ± ២០ មីក្រូម៉ែត្រ | ៥០០ មីក្រូម៉ែត្រ ± ២៥ មីក្រូម៉ែត្រ | |||||||||

| ការតំរង់ទិសបន្ទះ |

អ័ក្សក្រៅ៖ ៤.០° ឆ្ពោះទៅ < ១១២០ > ±០.៥° សម្រាប់ 4H-N, អ័ក្សលើ៖ <០០០១>±០.៥° សម្រាប់ 4H-SI | ||||||||||

| 4H-SI | ≤1 សង់ទីម៉ែត្រ-2 | ≤5 សង់ទីម៉ែត្រ-2 | ≤១៥ សង់ទីម៉ែត្រ-2 | ||||||||

| 4H-SI | ≥1E9 Ω·សង់ទីម៉ែត្រ | ≥1E5 Ω·សង់ទីម៉ែត្រ | |||||||||

| ទិសដៅសំប៉ែតចម្បង | {១០-១០} ±៥.០° | ||||||||||

| ប្រវែងសំប៉ែតបឋម | ៣២.៥ ម.ម ± ២.០ ម.ម | ||||||||||

| ប្រវែងរាបស្មើបន្ទាប់បន្សំ | ១៨.០ ម.ម ± ២.០ ម.ម | ||||||||||

| ទិសដៅរាបស្មើបន្ទាប់បន្សំ | ស៊ីលីកុនបែរមុខឡើងលើ៖ ៩០° CW។ ពីផ្ទៃរាបស្មើបឋម ±៥.០° | ||||||||||

| ការដកចេញគែម | ៣ ម.ម. | ||||||||||

| LTV/TTV/Bow/Warp | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| ភាពរដុប | មុខ C | ប៉ូឡូញ | Ra≤1 nm | ||||||||

| មុខស៊ី | ស៊ីអឹមភី | Ra≤0.2 nm | Ra≤0.5 nm | ||||||||

| ស្នាមប្រេះគែមដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ប្រវែងសរុប ≤ 10 ម.ម, តែមួយ ប្រវែង≤2 ម.ម | |||||||||

| បន្ទះ Hex ដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤0.1% | |||||||||

| តំបន់ពហុប្រភេទដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ផ្ទៃសរុប ≤3% | |||||||||

| ការរួមបញ្ចូលកាបូនដែលមើលឃើញ | ផ្ទៃសរុប ≤0.05% | ផ្ទៃសរុប ≤3% | |||||||||

| ស្នាមឆ្កូតលើផ្ទៃស៊ីលីកុនដោយពន្លឺអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ប្រវែងសរុប ≤1 *អង្កត់ផ្ចិតបន្ទះ | |||||||||

| បន្ទះសៀគ្វីគែមខ្ពស់ដោយពន្លឺអាំងតង់ស៊ីតេ | គ្មានអ្វីត្រូវបានអនុញ្ញាតទេ ≥0.2 ម.ម ទទឹង និងជម្រៅ | អនុញ្ញាត 5, ≤1 ម.ម ក្នុងមួយៗ | |||||||||

| ការចម្លងរោគលើផ្ទៃស៊ីលីកុនដោយអាំងតង់ស៊ីតេខ្ពស់ | គ្មាន | ||||||||||

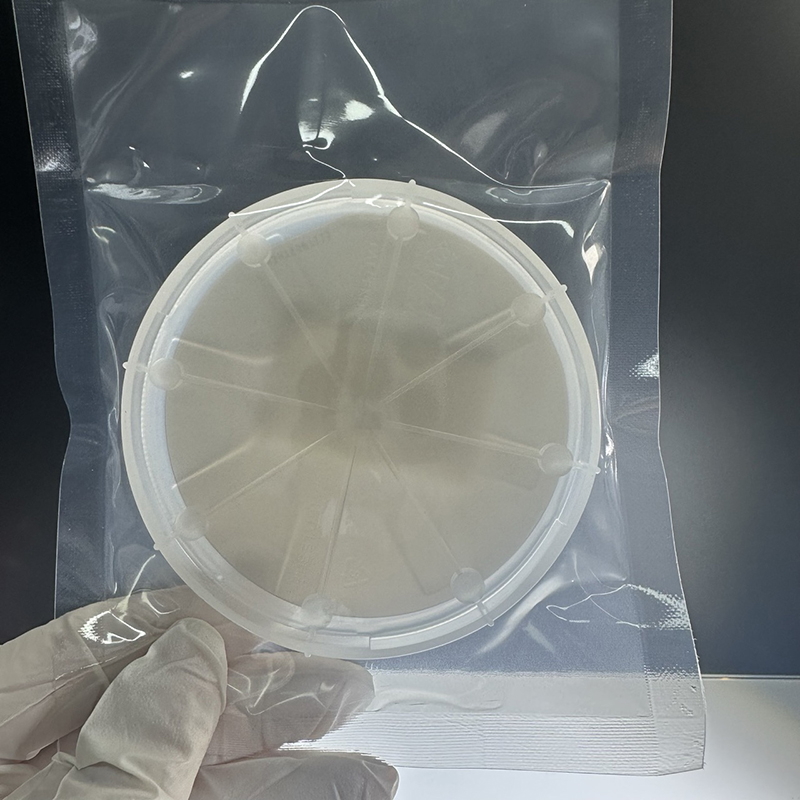

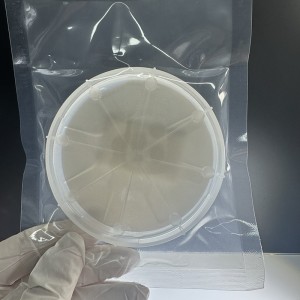

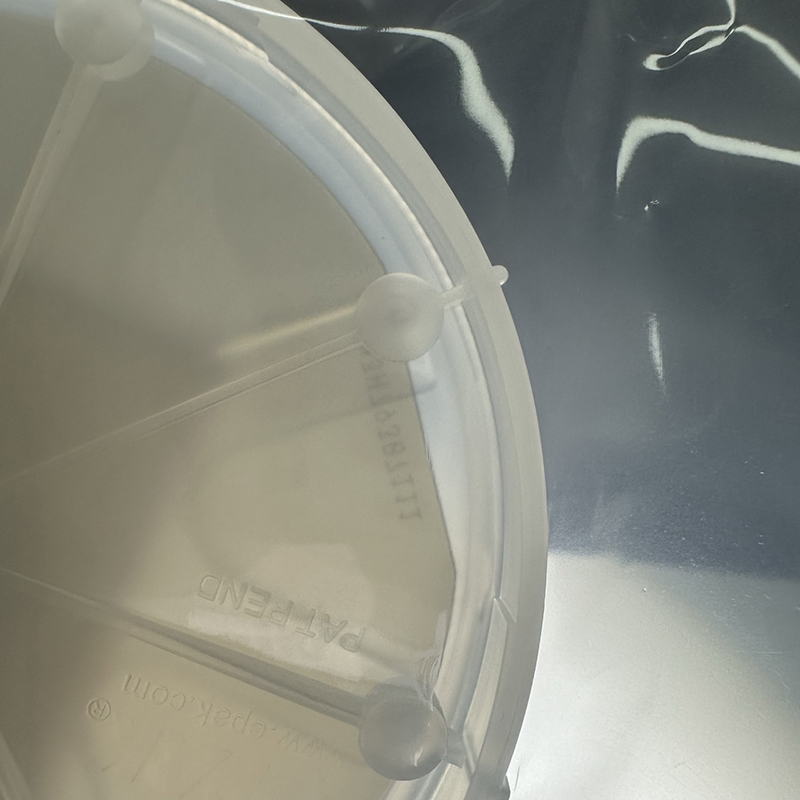

| ការវេចខ្ចប់ | កាសែតវ៉ាហ្វើរច្រើន ឬកុងតឺន័រវ៉ាហ្វើរតែមួយ | ||||||||||

ដ្យាក្រាមលម្អិត

ផលិតផលពាក់ព័ន្ធ

សរសេរសាររបស់អ្នកនៅទីនេះ ហើយផ្ញើវាមកយើង